In early summer, SiFive presented the P550 the fastest RISC-V cores for the time being before. Obviously, Intel was also convinced of this and will soon be offering corresponding designs to customers of the Intel Foundry Services (IFS). As early as 2022, Intel plans to offer the Horse-Creek RISC-V development platform, a process that allows cores or clusters and entire SoCs such as the P550 to be manufactured in 7 nm.

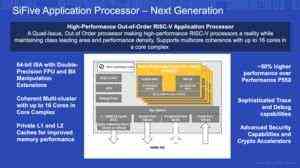

At the Linley conference, SiFive Vice President Shubu Mukherjee spoke about the successor. However, further details will not be available until the RISC-V Summit in December.

But let’s get to what SiFive has now presented. The as yet nameless core is said to be 50% faster than the P550. It is a 64-bit core with a double precision FPU (FP64) and private L1 and L2 cache. The P550 cores are combined in four-core clusters and use a shared L3 cache with a capacity of 4 MB. In the first quarter of 2022, the first customers should receive their chips based on the P550 from production (tape out).

| P550 | Next-gen P-Series | |

| L1 instruction cache | 32 kB | 64 – 128 kB |

| L1 data cache | 32 kB | 64 – 128 kB |

| L2 cache | 256 kB | up to 2MB |

| L3 cache | 1 – 4 MB | 1 – 16 MB |

| Core complex | up to 4 cores | up to 16 |

| Memory ports | 1x 128 or 256 bit | 4x 128 or 256 bit |

The successor to the P550 is set up more broadly, especially in terms of scaling. Up to 16 cores are used in a cluster. Accordingly, the shared L3 cache is increased to up to 16 MB. The L2 cache, which is exclusive for the individual cores, can now be up to 2 MB in size. Ultimately, the instruction and data cache are up to 128 kB in size – that is, up to four times as large. The actual structure of the cores or the computing units used and the fact that it is a 13-step pipeline with a triple issue in an out-of-order design obviously does not change anything. But we will find out details about this at the RISC-V Summit.

A design with 128 cores and more can be realized by connecting several of these clusters with one another. In addition to the CPU clusters, security components, a large last level cache and a translation engine can be connected to one another using Network on Chip (NOC). This results in quite complex chips with several (LP) DDR memory channels, numerous PCIe controllers and lanes as well as an external CXL connection via SiFive Chip2Chip-Link.

Even if RISC-V cores are already used in numerous chips, the breakthrough of these cores is still pending. IP providers such as SiFive are currently working quite successfully on expanding the RISC-V issue. The European Processor Initiative (EPI) works on accelerators based on RISC-V, which are to be used for the supercomputer developed in Europe.

At this point we want to continue our test of the Reference SiFive HiFive Unmatched. This is a developer platform for RISC-V.